Pertemuan 4 (Minimalisasi/Penyederhanaan Fungsi Boolean dan POSA/SOP)

Abstract

Modul ini membahas tentang hukum hukum pada Aljabar Boolean

Kompetensi

Mahasiswa diharapkan dapat mengetahui hukum pada aljabar boolean

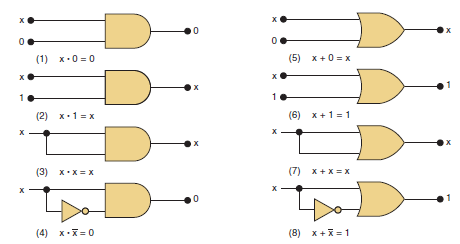

Teorema Boolean

Teorema Boolean berisi aturan aturan yang dapat digunakan untuk menyederhanakan persamaan logika dan rangkaian logika.

Teori ini hanya melibatkan satu variable

1. Jika sebuah varibel di AND kan dengan 0, maka hasilnya adalah 0

2. Jika sebuah variable di AND kan dengan 1, maka hasilnya adalah variable itu sendiri.

3. Dapat diuji dengan kasus berikut

X =0, maka 0 ∙ 0 =0

X =1, maka 1 ∙ 1 =1

4. Jika setiap X di AND kan dengan invers nya maka akan menghasilkan 0

X =0, maka 0 ∙ 1 =0

X =1, maka 1 ∙ 0 =0

5. Jika 0 ditambahkan dengan apapun, maka tidak akan mempengaruhi hasil akhirnya,

dan hasilnya akan sama dengan variable itu sendiri, baik dalam operasi biasa atau

dalam OR.

6. Setiap variable yang di OR kan dengan 1, maka hasilnya akan selalu 1.

X =0, maka 0 + 1 =1

X =1, maka 1 + 1 =1

7. Dapat diuji dengan memeriksa kedua nilai dari X

X =0, maka 0 + 0 =0

X =1, maka 1 + 1 =1

8. Dapat diuji dengan cara yang sama

X =0, maka 0 + 1 =1

X =1, maka 1 + 0 =1

Teorema Multivariabel

Hukum komutatif mengindikasikan bahwa urutan dua variable dalam operasi OR atau AND

tidak penting, karena hasilnya sama

Hukum asosiatif menyatakan bahwa kelompok variable dalam operasi OR atau AND tidak

penting, karena hasilnya sama.

Hukum Distributif

Teorema Demorgan

Teorema ini ada 2 yaitu :

Teori 16 menyatakan bahwa penjumlahan dua variable (OR) yang diinvers, maka hasil nya sama dengan setiap variable diinvers dan di AND kan.

Teori 17 menyatakan bahwa penjumlahan dua variable (AND) yang diinvers, maka hasil nya sama dengan setiap variable diinvers dan di OR kan.

UNIVERSALITY OF NAND GATES AND NOR GATES

NAND GATE

Semua persamaan Boolean terdiri dari berbagai kombinasi dari operasi dasar OR, AND dan INVERT. Setiap persamaan dapat diimplementasikan menggunakan gerbang OR, gerbang AND dan INVERTER. Sehingga memungkinkan untuk mengimplementasikan setiap persamaan logika menggunakan NAND gate, karena Gerbang NAND merupakan kombinasi yang dapat digunakan dalam operasi Boolean OR, AND dan INVERT.

Gambar a.

Gerbang NAND memiliki 2 input dimana kedua inputnya berasal dari variable A. dalam hal ini Gerbang NAND berindak sebagai INVERTER karena outputnya

Gambar b.

2 Gerbang NAND yang terhubung sehingga menghasilkan operasi AND. Gerbang NAND kedua berfungsi sebagai INVERTER untuk merubah seperti fungsi AND yang diinginkan.

Gambar c.

Operasi OR dapat diimplementasikan menggunakan gerbang NAND yang dihubungkan seperti Gambar diatas. Gerbang NAND 1 dan 2 digunakan sebagai INVERTER untuk membalik input, sehingga hasil akhir output dapat

disederhanakan menjadi menggunakan teori demorgan.

NOR GATE

Seperti halnya Gerbang NAND, dapat digunakan gerbang NOR.

Gambar a.

Gerbang NOR memiliki 2 input dimana kedua inputnya berasal dari variable A. dalam hal ini Gerbang NOR betrindak sebagai INVERTER karena outputnya

Gambar b.

2 Gerbang NOR yang terhubung sehingga menghasilkan operasi OR. Gerbang NOR kedua berfungsi sebagai INVERTER untuk merubah seperti fungsi OR yang diinginkan.

Gambar c.

Operasi AND dapat diimplementasikan menggunakan gerbang NOR yang dihubungkan seperti Gambar diatas. Gerbang NOR 1 dan 2 digunakan sebagai INVERTER untuk membalik input, sehingga hasil akhir output dapat disederhanakan menjadi menggunakan teori demorgan.

ALTERNATE LOGIC‐GATE REPRESENTATIONS

5 gerbang logika dasar (AND, OR, INVERTER, NAND dan NOR) memiliki standar symbol yang digunakan pada diagram rangkaian logika. Tetapi terkadang kita menemukan beberapa rangkaian digital yang menggunakan symbol sendiri yang merupakan symbol logika alternative.

Logic‐Symbol Interpretation

Ketika line input atau output pada sebuah rangkaian logika tidak memiliki bubble (lingkaran), maka line tersebut dikatan aktif HIGH. Dam jika line input atau output memiliki buble, maka line tersebut active LOW.

Gambar diatas menunjukkan symbol standard gerbang NAND. Symbol standar memiliki sebuah buble pada outputnya dan tidak memiliki bubble pada inputnya. Gerbang NAND ini memiliki output active LOW dan input aktif HIGH. Operasi logika ini dinyatakan dengan symbol : The output goes LOW only when all of the inputs are HIGH.

IEEE/ANSI STANDARD LOGIC SYMBOLS

- Simbol segi empat yang menggunakan sebuah segitiga sama dengan bubble pada symbol tradisional yang menyatakan invers dari logic level. Kehadiran segitiga menunjukkan apakah input atau output aktif LOW atau aktif HIGH

- Notasi khusus yang berada didalam symbol segi empat menjelaskan relasi logika antara input dan output :

1. “1” -> menunjukkan Inverter dan hanya memiliki 1 input.

2. “&” -> symbol AND yang berarti output aktif HIGH, jika semua inputnya aktif HIGH

3. >1 -> Gerbang OR, dimana output aktif HIGH jika salah satu atau semua inputnya aktif HIGH. - Simbol segiempat NAND dan NOR sama dengan symbol AND dan OR, dengan menambahkan segitiga invers pada outputnya.

Tugas!

Buatlah 2 Soal dan jawaban untuk Komutatif, Asosiatfi, dan Distributif

Daftar Pustaka

Ronald J. Tocci, Neal S.Widmer, Gregory L. Moss, Digital Systems Principles and Applications TENTH EDITION, 2007, Pearson Education International

SOP dan POS

Abstract

Modul ini membahas tentang penyederhanaan dengan Sum of Product dan Product of SUM

Kompetensi

Mahasiswa diharapkan melakukan penyederhanaan persamaan dengan menggunakan SOP dan POS

SUM‐OF‐PRODUCTS FORM

Metoda penyederhanaan rangkaian logika salah satunya adalah SOP (sum of products).

Contoh:

Setiap pernyataan dalam bentuk sum of products terdiri dari dua atau lebih operasi AND yang semuanya di OR kan.

PRODUCTS OF SUM FORM

Bentuk persamaan logika juga menggunakan POS (products of sum). Terdiri dari 2 atau lebih operasi OR yang kemudian di AND kan.

Contoh:

ALGEBRAIC SIMPLIFICATION

Sebuah pernyataan Boolean dapat kita sederhanakan bentuknya dengan menggunakan banyak cara, pernyataan yang baru digunakan untuk mengimplementasikan sebuah rangkaian yang sama dengan rangkaian asli, tetapi memiliki gerbang dan koneksi yang lebih sedikit.

Contoh :

Hasil Penyederhanaan :

Contoh:

Persamaan :

Langkah langkah :

Menggunakan teori demorgan -> menghasilkan bentuk SOP

Karena :

maka,

Rangkaian Sederhana :

Complete Design Procedure

Setiap masalah logika dapat diselesaikan dengan langkah langkah sebagai berikut :

1. Interpret the problem and set up a truth table to describe its operation.

2. Write the AND (product) term for each case where the output is 1.

3. Write the sum-of-products (SOP) expression for the output.

4. Simplify the output expression if possible.

5. Implement the circuit for the final, simplified expression.

Contoh :

Rancanglah sebuah rangkaian logika yang memiliki 3 input A, B dan C, dimana output akan menjadi HIGH hanya pada saat semua input mayoritas adalah HIGH.

Solusi

1. Menterjemahkan masalah dan membuat table kebenaran.

Output = 1 apabila mayoritas input adalah 1 (2/lebih input), dan yang lain output = 0

2. Membuat persamaan AND untuk output = 1

3. Menulis persamaan sum of products untuk output

4. Menyederhanakan persamaan

5. Implementasi rangkaian untuk persamaan terakhir

KARNAUGH MAP METHOD

Karnaugh map (K map) merupakan tool grafis yang digunakan untuk menyederhanakan persamaam logika atau untuk melakukan konversi sebuah table kebenaran menjadi rangkaian logika yang lebih sederhana.

Contoh

Peta karnaugh 2 variabel

Peta karnaugh 3 variabel

Peta karnaugh 4 variabel

Persamaan output X dapat disederhanakan dengan cara membuat kotak pada Kmap untuk yang berisi 1. Proses ini disebut dengan looping

Looping -> 2

Looping -> 4

Looping -> 8

Prosedure penyederhanan

Step 1 Construct the K map and place 1s in those squares corresponding to the 1s in the truth table. Place 0s in the other squares.

Step 2 Examine the map for adjacent 1s and loop those 1s that are not adjacent to any other 1s. These are called isolated 1s.

Step 3 Next, look for those 1s that are adjacent to only one other 1. Loop any pair containing such a 1.

Step 4 Loop any octet even if it contains some 1s that have already been looped.

Step 5 Loop any quad that contains one or more 1s that have not already been looped, making sure to use the minimum number of loops.

Step 6 Loop any pairs necessary to include any 1s that have not yet been looped, making sure to use the minimum number of loops.

Step 7 Form the OR sum of all the terms generated by each loop.

Contoh

TUGAS !!

Rancanglah sebuah rangkaian logika yang memiliki 4 input A, B, C, dan D dimana output akan menjadi HIGH hanya pada saat semua input mayoritas adalah HIGH.

DAFTAR PUSTAKA

Ronald J. Tocci, Neal S.Widmer, Gregory L. Moss, Digital Systems Principles and Applications TENTH EDITION, 2007, Pearson Education International