Pertemuan 12 (Rangkaian Sekuensial – Counter/Pencacah)

Tujuan Pembelajaran

1. Membedakan perilaku dan rangkaian pencacah sinkron dan asinkron

2. Merancang dan menganalisis rangkaian pencacah naik/turun sinkron/asinkron serta menganalisisnya

3. Merancang, menganalisis dan menguji implementasi rangkaian sekuensial menggunakan IC TTL

12.1 Pendahuluan

Rangkaian counter ini dapat digunakan melakukan beberapa fungsi, misalnya :

– Menghitung kejadian dari suatu event

– Membangkitkan interval waktu untuk mengontrol pekerjaan-pekerjaan (task) di sistem digital

– Menghitung waktu mundur antar event

– Menyediakan alamat baru di pencacah program (PC)

Rangkaian counter yang paling sederhana dapat dibuat dengan menggunakan flip-flop T

– Flip-Flop T secara natural cocok untuk diimplementasikan di operasi pencacahan

Pencacah Sinkron dan Asinkron

– Pencacah asinkron dibentuk dengan memberikan sinyal Clk ke terminal detak satu flip-flop

— Masukan detak untuk flip-flop berikutnya diperoleh dari keluaran flip-flop sebelumnya (efek serupa RCA)

— Lambat karena sumber Clk merambat dari satu flip-flop ke flip-flop lainnya

Pencacah sinkron dibentuk dengan memberikan sinyal Clk ke semua flip-flop di waktu yang sama

– Semua flip-flop menggunakan sumber detak yang sama

– Mempunyai respon yang lebih cepat daripada pencacah asinkron

12.2 Pencacah Asinkron

Pencacah Naik dengan Flip-Flop T

Pencacah 3-bit yang dapat mencacah 0 sampai 7 atau pencacah module-8

– Masukan clock untuk ketiga flip-flop dikoneksikan secara kaskade

— flip-flop pertama terkoneksi ke Clock

— flip-flop berikutnya, sinyal clocknya didrive dari keluaran Q flip-flop sebelumnya

— Rangkaian seperti ini disebut sebagai pencacah asinkron atau pencacah ripple

Masukan T tiap flip-flop dikoneksikan ke konstan 1

– State tiap flip-flop akan dibalik (toggle) setiap transisi naik clocknya

Diagram Pewaktuan Pencacah Naik

Nilai Q0 akan toggle setiap clock cycle

– Perubahan terjadi setelah transisi naik sinyal clock

Nilai Q1 akan toggle setelah transisi turun dari Q0, demikian juga Q2

Nilai Q2 Q1 Q0 menunjukkan nilai pencacahnya

Pencacah Turun dengan Flip-flop T

Mirip dengan rangkaian pencacah naik, kecuali masukan clock flip-flop kedua dan seterusnya berasal dari

keluaran Q flip-flop sebelumnya

Diagram Pewaktuan Pencacah Turun

Nilai Q0 akan toggle setiap clock cycle

– Perubahan terjadi setelah transisi naik sinyal clock

Nilai Q1 akan toggle setelah transisi naik dari Q1, demikian juga Q2

Latihan

Desain pencacah naik/turun 3-bit menggunakan flip-flop T. Sebuah masukan kontrol Up=Down harus disertakan.

Jika Up=Down = 0 rangkaian berfungsi sebagai pencacah naik. Jika Up=Down = 1 rangkaian berfungsi

sebagai pencacah turun.

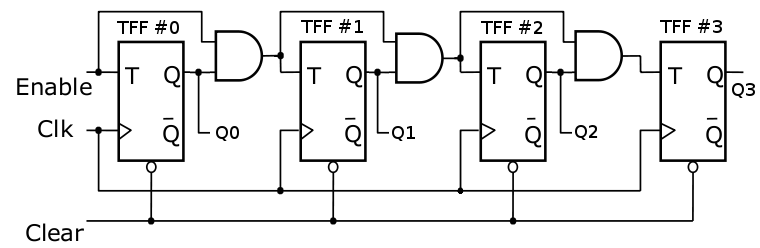

12.3 Pencacah Sinkron

Dapat dibentuk dengan TFF

Perilaku Pencacah Naik

masukan T tiap TFF akan bernilai sebagai berikut:

Implementasi rangkaian pencacah sinkron tersebut membutuhkan gerbang AND.

– Masukan T0 dihubungkan logika 1, sehingga Q0 akan membalik setiap transisi naik Clk

– Masukan T1 dihubungkan dengan Q0

– Masukan T2 membutuhkan gerbang AND-2 untuk memperoleh Q0Q1

– Masukan T3 membutuhkan gerbang AND-3 untuk memperoleh Q0Q1Q2

Masalah fan-in: pencacah n bit akan membutuhkan gerbang AND n – 1

Faktorisasi untuk mengatasi fan-in

Diagram Pewaktuan

Pencacah Naik n-Bit

Untuk sebarang pencacah naik n bit, rangkaiannya dapat dibentuk dengan persamaan masukan Tn sebagai berikut:

Pencacah Sinkron dengan Enable dan Clear

12.4 Pencacah Sinkron dengan DFF

Pencacah akan mempunyai urutan nilai 0, 1, 2, 3, · · · ; 15, 0, 1; · · ·

Nilai pencacah ini diberikan oleh keluaran DFF Q3Q2Q1Q0

Pencacah akan aktif saat Enable = 1. Saat Enable = 0 maka nilai pencacah tidak berubah

– Nilai Q0 akan membalik (toggle) setiap transisi naik Clk. Agar Q0 membalik di transisi naik Clk berikutnya, maka nilai D0 harus bernilai Q0 saat Enable = 1 . Persamaannya adalah D0 = Q0 ⊕ Enable

– Nilai Q1 akan membalik setelah nilai Q0 = 1. Agar Q1 membalik di transisi naik Clk berikutnya, maka nilai D1 harus bernilai Q1 saat Q0 = 1 dan Enable = 1 . Persamaannya adalah D1 = Q1 ⊕ Q0 · Enable

I Nilai Q2 akan membalik setelah nilai Q1 Q0 = 11. Agar Q2 membalik di transisi naik Clk berikutnya, maka nilai D2 harus bernilai Q2 saat Q1 = 1, Q0 = 1 dan Enable = 1 . Persamaannya adalah D2 = Q2 ⊕ Q1 · Q0 · Enable

I Nilai Q3 akan membalik setelah nilai Q2 Q1 Q0 = 111. Agar Q3 membalik di transisi naik Clk berikutnya, maka nilai D3 harus bernilai Q3 saat Q2 = 1, Q1 = 1, Q0 = 1 dan Enable = 1. Persamaannya adalah D3 = Q3 ⊕ Q2 · Q1 · Q0 · Enable

Untuk pencacah yang lebih besar, masukan D di tiap DFF bernilai Di = Qi ⊕ Qi-1 · Qi-2 · · · Q1 · Q0 · Enable

-> masalah fan-in

Rangkaian Pencacah Sinkron DFF

Rangkaian Pencacah Sinkron dengan Load Paralel

12.5 IC TTL Pencacah

IC 74393: Dual Pencacah Asinkron 4 Bit

IC 74393: Fungsi Logika

IC 74193: Dual Pencacah Sinkron 4 Bit, Naik/Turun

IC 74193: Fungsi Logika

IC 74193: Perilaku

Pencacah Sinkron n x 4 Bit (Menggunakan 74193)

Ringkasan Kuliah

Yang telah kita pelajari tentang rangkaian sekuensial adalah:

– Elemen rangkaian sekuensial berupa latch dan flip-flop:

— Latch: RS-latch, D-latch, gated latch

— Flip-flop : master-slave D flip-flop, edge-trigerred flip-flop, T flip-flop dan JK flip-flop

— Perbedaan antara latch dan flip-flop

– Register dan pencacah

— Register data dan register geser

— Pencacah asinkron dan sinkron

Tugas

Kumpulkan 1 pdf Materi tentang Counter beserta implementasi dalam dunia sistem komputer (wajib ada daftar pustaka)

Daftar Pustaka

1. Datasheet CD4043BE (Texas): Quad Latch SR NOR.

http://www.ti.com/lit/gpn/CD4043B

2. Datasheet CD4044BE (Texas), 54LS279 , 74LS279: Quad Latch SR NAND.

http://www.ti.com/lit/gpn/CD4044B

3. Datasheet SN74LS74A: Dual D-type Positive-Edge-Trigerred Flip-Flops with Preset and Clear.

http://www.ti.com/lit/gpn/SN74LS74A