Pertemuan 6 (Rangkaian Sekuensial – (Flip-Flop)

Daftar Isi (Table Of Content)

Tujuan Pembelajaran

1. Mahasiswa dapat mengetahui dan memahami FLIP-FLOP D (MASTER SLAVE D Flip-Flop)

2. Mahasiswa dapat mengetahui dan memahami FLIP-FLOP TOGGLE (T)

3. Mahasiswa dapat mengetahui dan memahami FLIP-FLOP JK

4. Mahasiswa dapat mengetahui dan memahami IC TTL FLIP-FLOP

1. Pengantar Rangkaian Sekuensial Flip-Flop:

1.1 Definisi flip-flop dan peranannya dalam rangkaian sekuensial.

Flip-flop adalah suatu elemen logika dalam rangkaian elektronik yang berfungsi sebagai memori atau penyimpan sementara informasi digital. Flip-flop dapat menyimpan satu bit data, yang dapat bernilai 0 atau 1. Flip-flop digunakan dalam rangkaian sekuensial untuk menyimpan dan mengubah keadaan (state) sistem secara berurutan berdasarkan input dan kondisi sebelumnya.

Peran utama flip-flop dalam rangkaian sekuensial adalah sebagai elemen penyimpanan yang memungkinkan sistem untuk memiliki memori dan mengingat keadaan sebelumnya. Dengan adanya flip-flop, rangkaian sekuensial dapat memiliki perilaku yang dinamis dan dapat merespons input dengan cara yang tergantung pada keadaan sebelumnya.

Flip-flop memungkinkan implementasi berbagai elemen penting dalam desain rangkaian sekuensial, seperti register, counter, dan memori. Dalam kombinasi dengan gerbang logika dan rangkaian kontrol yang tepat, flip-flop memungkinkan pengembangan sistem elektronik yang kompleks, termasuk mikroprosesor, komunikasi digital, dan perangkat digital lainnya.

Selain itu, flip-flop juga berperan dalam sinkronisasi dan pengaturan waktu dalam rangkaian sekuensial. Dengan menggunakan sinyal clock, flip-flop dapat diaktifkan dan memperbarui keadaan penyimpanannya hanya pada saat yang ditentukan, sehingga memungkinkan koordinasi yang tepat antara berbagai komponen dalam sistem sekuensial.

Dalam rangkaian sekuensial yang lebih kompleks, kombinasi dan pengaturan flip-flop yang tepat dapat menghasilkan pemrosesan informasi yang lebih kompleks, seperti penyimpanan data jangka panjang, penghitungan, pembangkitan sinyal kontrol, dan banyak lagi.

1.2 Konsep dasar memori dan penyimpanan informasi.

2. Jenis-Jenis Flip-Flop:

2.1 Flip-Flop SR (Set-Reset):

A. Prinsip kerja flip-flop SR.

Prinsip kerja flip-flop SR (Set-Reset) didasarkan pada penggunaan dua input: input Set (S) dan input Reset (R). Flip-flop SR menyimpan satu bit data dan memiliki dua keadaan yang mungkin: keadaan Set dan keadaan Reset.

Berikut adalah prinsip kerja flip-flop SR:

- Keadaan awal: Flip-flop SR memiliki dua keadaan awal yang mungkin, yaitu keadaan Set (S=1, R=0) atau keadaan Reset (S=0, R=1). Keadaan ini menentukan nilai awal yang disimpan dalam flip-flop.

- Input Set (S): Ketika input Set (S) diberikan sinyal logika 1, keadaan flip-flop akan berubah menjadi keadaan Set (S=1, R=0). Dalam keadaan ini, keluaran flip-flop (Q) akan menjadi 1, dan keluaran komplementer (Q̅) akan menjadi 0.

- Input Reset (R): Ketika input Reset (R) diberikan sinyal logika 1, keadaan flip-flop akan berubah menjadi keadaan Reset (S=0, R=1). Dalam keadaan ini, keluaran flip-flop (Q) akan menjadi 0, dan keluaran komplementer (Q̅) akan menjadi 1.

- Input yang tidak valid: Ketika kedua input Set (S) dan Reset (R) diberikan sinyal logika 0 secara bersamaan (S=0, R=0), keadaan flip-flop akan tidak terdefinisi (indeterminate) atau mengalami konflik (race condition). Keadaan ini harus dihindari karena dapat menyebabkan keluaran yang tidak diinginkan.

- Keadaan tetap: Setelah flip-flop berada dalam keadaan Set atau Reset, keadaan tersebut akan tetap berlaku sampai ada perubahan input. Dengan kata lain, keadaan flip-flop akan “mengingat” keadaan sebelumnya sampai ada perubahan input yang mempengaruhinya.

Prinsip kerja flip-flop SR juga dapat dinyatakan dalam bentuk tabel kebenaran, yang menjelaskan hubungan antara input (S dan R) dengan keluaran (Q dan Q̅). Berdasarkan tabel kebenaran ini, dapat dikembangkan diagram waktu yang menggambarkan perubahan keadaan flip-flop SR seiring dengan perubahan input.

Penting untuk diingat bahwa flip-flop SR asinkron, yang berarti perubahan keadaan terjadi segera setelah ada perubahan pada input. Hal ini dapat menyebabkan masalah seperti glitch dan masalah metastabilitas, yang harus diperhatikan dalam desain rangkaian yang menggunakan flip-flop SR.

B. Tabel kebenaran dan diagram waktu flip-flop SR.

Berikut adalah tabel kebenaran dan diagram waktu untuk flip-flop SR:

Tabel Kebenaran Flip-Flop SR:

Keterangan:

- S: Input Set

- R: Input Reset

- Q(t): Keluaran saat ini

- Q(t+1): Keluaran berikutnya

- X: Tidak valid (diharapkan untuk dihindari)

Diagram Waktu Flip-Flop SR:

C. Aplikasi dan kegunaan flip-flop SR.

D. Kelemahan dan masalah yang terkait dengan flip-flop SR.

2.2 Flip-Flop D (Data):

Prinsip kerja flip-flop D.

Tabel kebenaran dan diagram waktu flip-flop D.

Implementasi flip-flop D dengan gerbang logika.

Aplikasi dan kegunaan flip-flop D.

Perbedaan antara flip-flop D dengan flip-flop SR.

2.3 Flip-Flop JK (Jack-Kilby):

Prinsip kerja flip-flop JK.

Tabel kebenaran dan diagram waktu flip-flop JK.

Implementasi flip-flop JK dengan gerbang logika.

Aplikasi dan kegunaan flip-flop JK.

Perbedaan antara flip-flop JK dengan flip-flop SR dan D.

2.4 Flip-Flop T (Toggle):

Prinsip kerja flip-flop T.

Tabel kebenaran dan diagram waktu flip-flop T.

Implementasi flip-flop T dengan gerbang logika.

Aplikasi dan kegunaan flip-flop T.

Perbedaan antara flip-flop T dengan flip-flop SR, D, dan JK.

3. Sinkronisasi Flip-Flop:

Sinkronisasi flip-flop dengan clock.

Upaya untuk menghindari masalah metastabilitas.

Timing diagram dan penjelasan sinkronisasi flip-flop.

Penerapan Rangkaian Sekuensial Flip-Flop:

Penerapan rangkaian sekuensial menggunakan flip-flop.

Contoh penggunaan flip-flop dalam register, counter, dan memori.

Kesimpulan:

Ringkasan materi yang telah dipelajari.

Pentingnya pemahaman tentang rangkaian sekuensial flip-flop dalam desain digital.

Referensi tambahan untuk memperdalam pemahaman.

Pastikan untuk menggambarkan diagram waktu, tabel kebenaran, dan contoh penggunaan untuk setiap jenis flip-flop yang dibahas. Selain itu, berikan penekanan pada perbedaan antara jenis flip-flop yang berbeda dan kapan menggunakan jenis flip-flop yang tepat dalam desain rangkaian sekuensial.

10.1 Pendahuluan

Latch

Rangkaian latch (gated) merupakan level-sensitive

-State dapat berubah lebih dari sekali selama periode ‘aktif’ dari sinyal clock

–Untuk logika positif, periode aktif adalah saat clk=1. Dan sebaliknya

Flip-flop

-Elemen penyimpan 1 bit

-Statenya berubah hanya sekali dalam satu periode clock

-Tipe: master-slave ip-op dan edge-triggered flip-flop

-Jenis: DFF (data), TFF (toggle) dan JKFF

10.2 FLIP-FLOP D (MASTER SLAVE D Flip-Flop)

Dibentuk dari 2 buah gated D latch (38 transistor CMOS): sebagai master dan slave

-master mengubah statenya saat clock = 1

-slave mengubah statenya saat clock = 0

I Analisis diagram pewaktuan

10.2.1 Perilaku

Saat clock=1, master melihat nilai dari sinyal masukan D, slave tidak berubah

-Qm mengikuti perubahan D, dan Qs konstan

Saat clock=0, master berhenti mengikuti perubahan nilai masukan D, sebaliknya slave merespon masukan Qm dan mengubah statenya

-Karena Qm tidak berubah selama clock=0, slave hanya mengubah statenya sekalis aja selama satu siklus clock

Dari sudut pandang keluaran

-Rangkaian mengubah Qs (keluaran ip-op) di titik transisi negatif sinyal clock (perubahan dari 1->0)

-Disebut negative-edge-triggered D Flip-Flop

Simbol dan Karakteristik DFF Transisi Turun

10.2.2 Efek Delay Propagasi

Sebelumnya efek delay propagasi diabaikan

-Dalam prakteknya, delay ini perlu diperhatikan

Di master-slave D ip-op (negative-edge)

-nilai D harus tidak berubah (stabil) saat clock berubah dari 1 ke 0 (transisi turun)

–Waktu minimum dimana sinyal D harus stabil sebelum transisi clock turun disebut setup time (tsu)

–Waktu minimum dimana sinyal D harus stabil setelah transisi clock disebut hold time (th)

–Nilai tipikal di CMOS: tsu = 3ns dan th = 2ns

10.2.3 Positive-Edge-triggered DFF

I Rangkaian berfungsi sama dengan master-slave D ip-op dapat dibentuk dengan 6 gerbang NAND (24 transistor)

Saat clock = 0, keluaran gerbang 2 dan 3 tinggi

-P1 = P2 = 1, keluaran latch tidak berubah, berada di present statenya

-P3 = D dan P4 = D

Saat clock = 1, nilai P3 dan P4 ditransmisikan lewat gerbang 2 dan 3

10.2.4 Perilaku Positive DFF

10.2.5 Disiplin Pewaktuan

Untuk dapat beroperasi dengan reliabel, P3 dan P4 harus stabel saat clock berubah dari 0 ke 1 (transisi naik)

-Setup time dari ip-op sama dengan delay dari masukan D lewat gerbang 4 dan 1 ke P3

-Hold time diberikan oleh delay lewat gerbang 3, sebab sekali P2 stabil, perubahan di D tidak akan berpengaruh

(mengubah state)

Harus dipastikan bahwa setelah clock berubah ke 1, setiap perubahan di D tidak akan mempengaruhi keluaran latch

selama clock=1

-Kasus 1: jika D=0 saat transisi naik clock, maka P2=0 yang akan membuat keluaran gerbang 4 sama dengan 1

selama clock=1, apapun nilai dari masukan D

-Kasus 2: jika D=1 saat transisi naik clock, maka P1=0 yang memaksa keluaran gerbang 1 dan 3 sama dengan 1, apapun nilai dari masukan D

-Sehingga, ip-op akan mengabaikan perubahan

Edge-triggered Flip-Flop (Positive-edge dan Negative-edge D Flip-Flop)

Dua tipe rangkaian:

-positive-edge triggered D flip-flop

–rangkaian merespon di transisi positif sinyal clock

-negative-edge triggered D flip-flop

–rangkaian merespon di transisi negatif sinyal clock

Membandingkan Elemen Penyimpan Data (Latch, Positive-edge DFF dan Negative-edge DFF)

I Elemen storage: Level-sensitive, positive-edge-sensitive, dan negative-edge-sensitive

Masukan Preset dan Clear di DFF

I Diinginkan untuk mengeset sebuah flip-flop (Q = 1) atau meng-clear-kannya (Q = 0)

I Flip-flop umumnya mempunyai masukan preset dan clear

I Input ini asinkron (tidak tergantung dari sinyal clock)

I Keluaran Q berubah seketika saat preset atau clear aktif (active-low)

I Jika Preset = 0, keluaran Q = 1

I Jika Clear = 0, keluaran Q = 0

Masukan Preset dan Clear (Negative-edge-trigerred DFF (transisi turun)

Simbol DFF Transisi Turun, Preset, Clear

Masukan Preset dan Clear (Posedge-triggered D flip-flop with Preset and Clear)

Simbol DFF Transisi Naik, Preset, Clear

10.3 FLIP-FLOP TOGGLE (T)

Menggunakan sebuah posedge D flip-flop dan rangkaian logika untuk mendrive masukannya

Feedback membuat sinyal masukan D sama dengan nilai Q atau Q di bawah kontrol sinyal T

-Saat T = 1 ! state rangkaian ‘toggle’ saat transisi clock naik

-Saat T = 0 ! statenya tetap

-Digunakan sebagai elemen di rangkaian pencacah

Rangkaian dan Diagram Pewaktuan TFF

Simbol dan Fungsi TFF

10.4 FLIP-FLOP JK

Flip-flop JK dapat diturunkan dari flip-flop D, dengan menggunakan 2 masukan J dan K, sehingga

D = JQ + KQ

Flip-flop JK mengkombinasikan perilaku flip-flop SR dan flip-flop T

-J = S dan K = R untuk semua nilai, kecuali untuk J = K = 1 (flip-flop SR)

-Jika J=K=1, flip-flop menbalik (toggle) statenya seperti flip-flop T

Dapat digunakan sebagai storage seperti DFF dan SR FF. Dan juga T FF dengan menghubungkan J dan K sebagai T

Rangkaian dan Diagram Pewaktuan JKFF

Simbol dan Fungsi TFF

Dapat digunakan sebagai elemen penyimpan 1 bit

-DFF: menghubungkan Data ke masukan J dan Data ke masukan K

TFF: menghubungkan Toggle ke J dan K

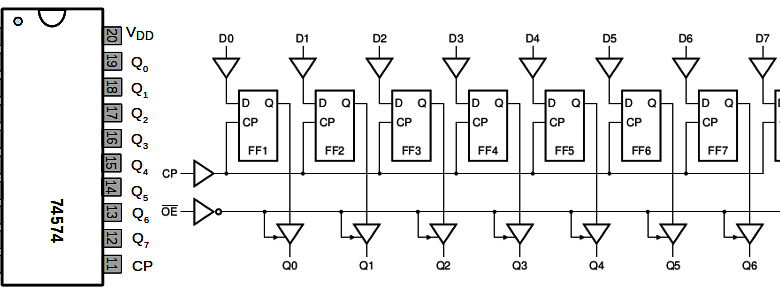

10.5 IC TTL FLIP-FLOP

IC 7474

Dual D-type Positive-Edge-Trigerred Flip-Flops with Preset and Clear

IC 7474: Rangkaian dan Fungsi

IC 74574: 8 DFF Transisi Naik, Tiga Keadaan

Tugas

Buat makalah Flip-flop (sebagai materi pembanding) kumpul dalam bentuk PDF

Daftar Pustaka

1. Givone DD. Digital principles and Design. Palgrave Macmillan; 2003.

2. Saha A, Manna N. Digital principles and logic design. Jones & Bartlett Learning; 2009 Jan 28.

3. Maini AK. Digital electronics: principles, devices and applications. John Wiley & Sons; 2007 Sep 27.

4. Singh AK. Digital Principles Foundation Of Circuit Design And Application. New Age International; 2006.

5. Leach DP, Malvino AP. Digital Principles and Applications. Glencoe/McGraw-Hill; 1994 May 1.